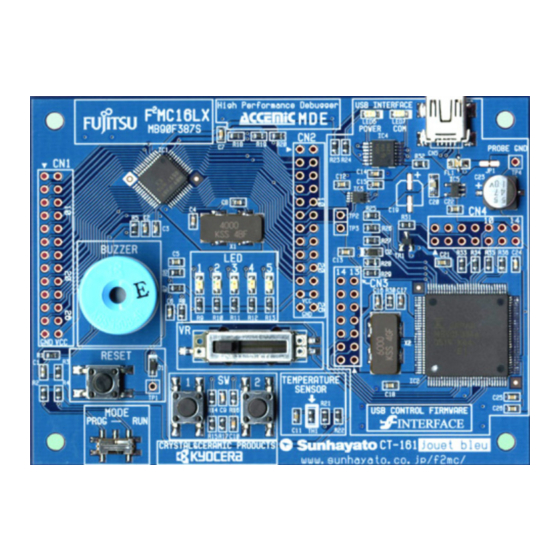

Fujitsu MB90460 Series Manuals

Manuals and User Guides for Fujitsu MB90460 Series. We have 1 Fujitsu MB90460 Series manual available for free PDF download: Hardware Manual

Fujitsu MB90460 Series Hardware Manual (739 pages)

F2MC-16LX 16-BIT MICROCONTROLLER

Brand: Fujitsu

|

Category: Microcontrollers

|

Size: 6.21 MB

Table of Contents

-

-

Cpu47

-

Memory Space48

-

Memory Maps50

-

Addressing52

-

Registers58

-

Prefix Codes76

-

-

-

Standby Mode117

-

Sleep Mode118

-

Stop Mode123

-

-

-

Interrupt133

-

-

-

-

Mode Setting177

-

Mode Data179

-

-

-

-

-

-

-

-

PWC Timer Pins455

-

Chapter 17 Uart

486-

Overview of UART487

-

UART Pins492

-

UART Registers494

-

UART Interrupts505

-

UART Baud Rates509

-

-

-

-

-

-

-

Appendix

646 -

Index

716